# 초고속 메모리 테스트를 위한 패턴 생성기 ASIC의 검증

# (Verification of a Pattern Generator ASIC for High-Speed Memory Test)

김정화\*, 정성후\*, 문병인\*\*

(Junghwan Kim, Sunghun Jung, and Byungin Moon<sup>©</sup>)

#### Abstract

Recently, with the development of memory-related technologies, interest in memory test equipment and test technologies is increasing, and research on a method of performing tests on high-capacity memory at high speed has been actively conducted. Among various memory test algorithms, March algorithm is widely used for memory testing because it has simple structure and high test coverage. A high-speed March pattern generator is necessary to perform March test of high-speed memory. This paper presents the verification results of a March pattern generator ASIC that was implemented in our previous work.

Keywords: Memory Test, March Algorithm, Pattern Generator, ASIC Verification

## I. 서론

최근 메모리의 수요가 폭발적으로 증가하고, 메모리 관련 기술의 발전에 따라 메모리의 성능 또한 크게 발전하고 있다[1]. 그러나 메모리의 발전에 비해 메모리의 결함을 진단하기 위한테스트 장비의 발전은 크게 뒤쳐지고 있는 실정이다. 메모리 결함으로 인한 문제는 메모리의 동작 속도가 올라감에 따라 더욱 크게 발생한다. 이에 최근 메모리 결함 테스트 장비 및 테스트 기술에 대한 주목도가 높아지고 있으며, 초고속으로 고용량 메모리에 대한 결함 진단 테스트를 수행하기 위한 방법에 대한 연구가 많이수행되고 있다[2-4]. 메모리 테스트 알고리즘 중 March 알고리즘의 경우 단순하면서도 다양한 종류의 결함을 진단할 수 있어 최근 메모리 테스트에 많이 활용되고 있다[5]. March 알고리즘은 MATS, MATS+, March A, March Y, March SR 등 여러 종류의 March 패턴 묶음으로 구성되며, 다양하고 많은 종류의 March 패턴을 사용하여 메모리의 결함을 정확하게 진단한다. 그러나.

March 패턴들을 테스트 장비 내의 메모리에 저장해두고 사용하는 방식으로는 선형 테스트 알고리즘의 결함 coverage를 일정 수준 이상으로 높이기 어렵고, 초고속으로 동작하는 메모리의 경우메모리 동작 속도에 비해 메모리 테스트를 위한 패턴 생성 속도가현저히 떨어지게 된다. 이에 본 연구진은 외부로부터 테스트 알고리즘에 따른 Word Oriented March (WOM) 패턴의 instruction들을 입력받아 초고속으로 March 패턴들을 생성하는 병렬 구조의 패턴 생성기 ASIC을 설계하였으며[6, 7], 본 논문을 통해 패턴 생성기 ASIC의 동작 검증 결과를 제시한다.

# Ⅱ. 하드웨어 구조

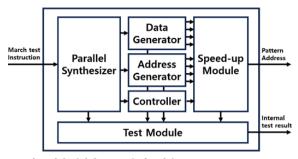

초고속 메모리 테스트를 위한 패턴 생성기 ASIC의 하드웨어 구조는 그림1과 같다. 패턴 생성기 ASIC은 크게 Parallel Synthesizer, Data Generator, Address Generator, Speed-up Module, Controller, Test Module로 구성된다.

1

- \* 경북대학교 대학원 전자전기공학부

- \*\* 경북대학교 대학원 전자전기공학부, 경북대학교 IT대학 전자공학부

- © Corresponding Author(E-mail: bihmoon@knu.ac.kr)

• 그림1. 패턴 생성기 ASIC의 하드웨어 구조

Parallel Synthesizer는 March 알고리즘에 따라 입력되는 명령어를 패턴 생성기 내부 Data Generator와 Address Generator를 제어하기 위한 내부 instruction으로 변환한다. 변환된 내부 instruction들은 March 알고리즘의 동작 순서에 맞게 저장되며, 메모리 테스트가 시작되면 내부 동작 주파수에 맞추어 Data Generator와 Address Generator에 전달된다. Data Generator와 Address Generator는 내부 instruction에 따라 각각 서로 다른 4개의 March 패턴과 메모리 주소값을 병렬적으로 생성한다. Speed-up Module은 Data Generator와 Address Generator에서 병렬적으로 생성된 패턴과 메모리 주소값을 빠른 동작 주파수에 맞게 다시 직렬화하여 출력한다. Controller는 패턴 생성기의 전반적인 동작을 제어하고, Test Module은 패턴 생성기 ASIC의 내부 동작 검증을 위해 사용된다.

# Ⅲ ASIC 동작 검증

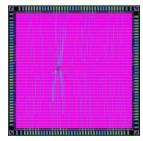

패턴 생성기 ASIC은 IDEC에서 지원하는 삼성 28nm MPW 프로그램을 통해 제작하였으며, 표1과 같은 ASIC 개발 flow에 따라 설계를 진행하였다. 최종 설계된 패턴 생성기 ASIC의 EDA Tool 상에서의 레이아웃 및 공정사를 통해 제작 완료된 ASIC의 실물은 그림2와 같으며, 설계 사양은 표2와 같다.

• 그림2. 패턴 생성기 ASIC 레이아웃 및 ASIC 실물

표1. ASIC 개발 flow

| Phase     | Task | Description                        |

|-----------|------|------------------------------------|

| Front-end | 1    | RTL Design & Function Simulation   |

|           | 2    | Synthesis                          |

|           | 3    | Design Rule Check                  |

|           | 4    | Formal Verification                |

|           | 5    | Pre-layout Static Timing Analysis  |

|           | 6    | Pre-layout Simulation with SDF     |

| Back-end  | 7    | Place & Route                      |

|           | 8    | RC Extraction                      |

|           | 9    | Post-layout Static Timing Analysis |

|           | 10   | Post-layout Simulation with SDF    |

|           | 11   | Static Power Analysis              |

|           | 12   | Physical Verification              |

표2. 패턴 생성기 ASIC 설계 사양

| Size      |      | $4 \times 4 \text{ mm}^2$ |  |  |

|-----------|------|---------------------------|--|--|

| Input     | I/O  | 1.8 V                     |  |  |

| Voltage   | Core | 1.1 V                     |  |  |

| Maximum   | I/O  | 200 MHz                   |  |  |

| Frequency | Core | 1 GHz                     |  |  |

| Gate cour | nt   | 13,336                    |  |  |

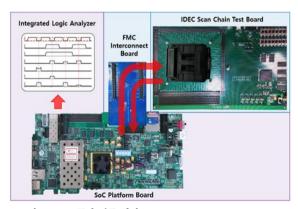

ASIC 동작 검증 환경은 그림3과 같이 IDEC Scan Chain Test Board, FMC Interconnect Board, SoC Platform Board로 구성되며, 패턴 생성기 ASIC의 동작 검증 방법은 다음과 같다.

• 그림3. ASIC 동작 검증 환경

• 그림4. 패턴 생성기 ASIC 동작 검증 결과

먼저, IDEC Scan Chain Test Board에 패턴 생성기 ASIC을 마운트하고, FMC Interconnect Board를 통해 IDEC Scan Chain Test Board와 SoC Platform Board를 서로 연결한다. SoC Platform Board는 March 알고리즘 명령어를 IDEC Scan Chain Test Board에 탑재된 패턴 생성기 ASIC에 전송하고, 패턴 생성기 ASIC에서 출력되는 March 패턴과 메모리 주소값은 FMC Interconnect Board를 통해 다시 SoC Platform Board로 전송된다. 최종적으로 SoC Platform Board의 ILA(Integrated Logic Analyzer)를 통해 패턴 생성기 ASIC에서 출력된 March 패턴 및 메모리 주소값에 대한 파형을 확인함으로써 패턴 생성기 ASIC의 동작을 검증한다.

패턴 생성기 ASIC의 동작 검증 결과는 그림4와 같으며, 입력으로 들어간 March 알고리즘 명령어에 따라 서로 다른 종류의 March 패턴과 선형적으로 증가하는 메모리 주소값이 순차적으로 출력되는 것을 확인할 수 있다.

### IV. 결론

본 연구를 통해 초고속 메모리 테스트를 위한 패턴 생성기 ASIC의 동작 검증을 수행하였다. ASIC 동작 검증을 통해 패턴 생성기 ASIC이 정상적으로 동작하는 것을 검증함으로써 패턴 생성기 ASIC 설계 내용의 무결성을 확인하였다. 개발된 패턴 생성기 ASIC은 높은 동작 주파수에서 테스트 패턴을 생성할 수 있어 초고속으로 동작하는 메모리의 테스트에 적용될 수 있으며, 메모리테스트 장비의 비용과 소모 전력을 크게 줄일 수 있다. 또한, 개발된 패턴 생성기 ASIC은 외부로부터 입력받은 March 알고리즘에따라 패턴을 생성하는 구조로, 모든 종류의 March 테스트에 대응하여 테스트 패턴을 생성할 수 있다.

### **ACKNOWLEDGMENT**

본 연구는 산업통상자원부(20019363)와 KSRC 지원 사업인 미래반도체소자 원천기술개발사업의 연구결과로 수행되었습니다. 본 연구는 IDEC에서 MPW와 EDA Tool을 지원받아 수행하 였습니다.

### 참고문헌

- [1] S. Shiratake, "Scaling and performance challenges of future DRAM," 2020 IEEE International Memory Workshop (IMW), pp. 1–3, May 2020.

- [2] A. Z. Jidin, R. Hussin, L. W. Fook, and M. S. Mispan, "A review paper on memory fault models and test algorithms," Bulletin of Electrical Engineering and Informatics, Vol. 10, no. 6, pp. 3083–3093, December 2021.

- [3] T. N. Kong, N. E. Alias, A. Hamzah, I. Kamisian, M. P. Tan, U. U. Sheikh, and Y. A. Wahab, "An Efficient March (5n) FSM-Based Memory Built-In Self Test (MBIST) Architecture," 2021 IEEE Regional Symposium on Micro and Nanoelectronics (RSM), pp. 76-79, August 2021.

- [4] W. Che, "FPGA-based memory test system design and test algorithm implementation," 2023 3rd International Conference on Electronic Information Engineering and Computer (EIECT), pp. 376–380, November 2023.

- [5] A. J. Van de Goor and I. B. Tlili, "March tests for word-oriented memories," In Proceedings Design, Automation and Test in Europe, pp. 501–508, February 1998.

- [6] 김정환, 송하윤, 문병인, "초고속 메모리 테스트를 위한 패턴 생성기", 한국반도체테스트학회학술발표대회 논문집, Vol. 24, pp. 154-156, June 2023.

- [7] 김정환, 송하윤, 정성훈, 문병인, "초고속 메모리 테스트를 위한 패턴 생성기의 ASIC 설계", Proceedings of KIIT Conference, pp. 207-207, November 2023.